http://zeptobars.ru/en/read/avalon-bitcoin-mining-unit-rig

PS. Я открыт, чтобы сделать фотографии любых других чипов пользовательских Bitcoin. Bitfury находится рядом на поезде. BFL, кто?

|

10 июня 2013, 8:52:48 PM

10 июня 2013, 8:52:48 PM

|

# 1 |

|

Сообщений: 56

цитировать ответ |

Взлом Биткоин адресов.

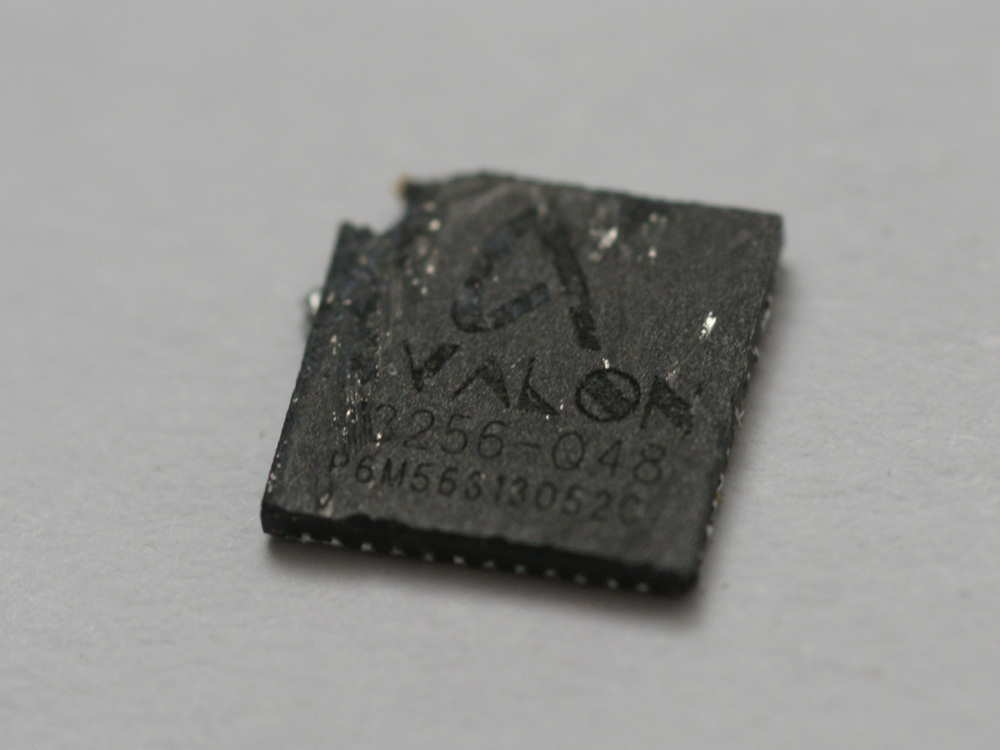

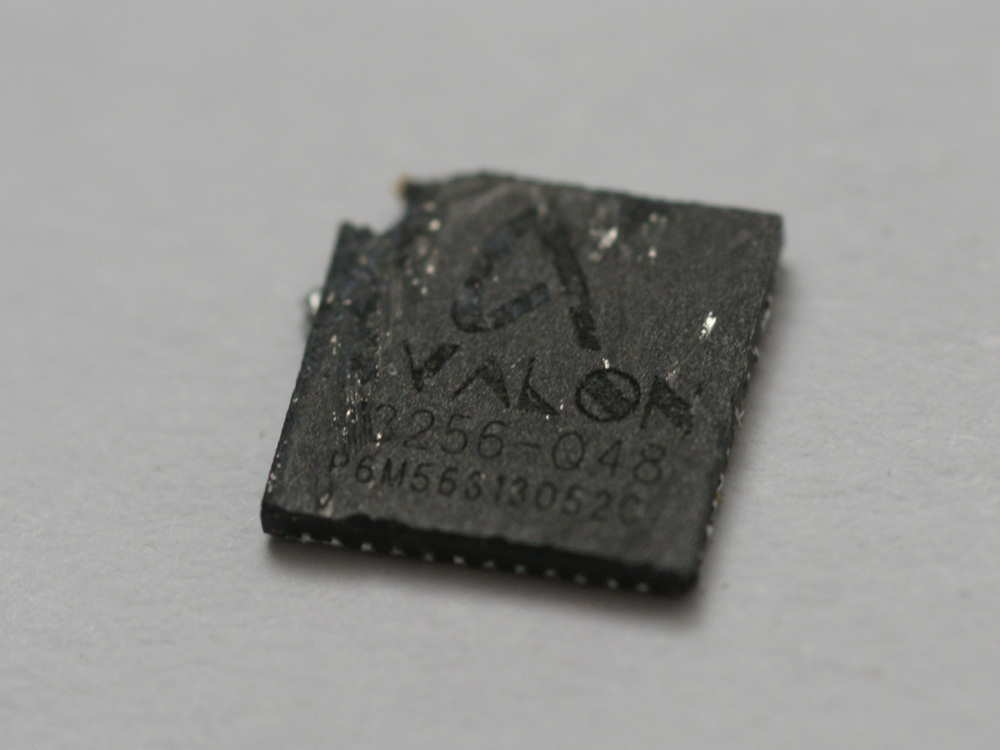

500 Биткоинов взломаны в "мозговом кошельке" с паролем "bitcoin is awesome" Адрес кошелька: 14NWDXkQwcGN1Pd9fboL8npVynD5SfyJAE Приватный ключ: 5J64pq77XjeacCezwmAr2V1s7snvvJkuAz8sENxw7xCkikceV6e подробнее... Всем кто хочет заработать Биткоины без вложений - рекомендую сайт http://bitcoin-zarabotat.ru Слегка поврежденный чип был извлечен из живой добычи вышки (спасибо за чип идет на наше собратом форуме needbmw членов):

http://zeptobars.ru/en/read/avalon-bitcoin-mining-unit-rig PS. Я открыт, чтобы сделать фотографии любых других чипов пользовательских Bitcoin. Bitfury находится рядом на поезде. BFL, кто? |

|

|

10 июня 2013, 9:02:29 PM

10 июня 2013, 9:02:29 PM

|

# 2 |

|

Сообщений: 50

цитировать ответ |

|

|

|

10 июня 2013, 9:05:29 PM

10 июня 2013, 9:05:29 PM

|

# 3 |

|

Сообщения: 2082

цитировать ответ |

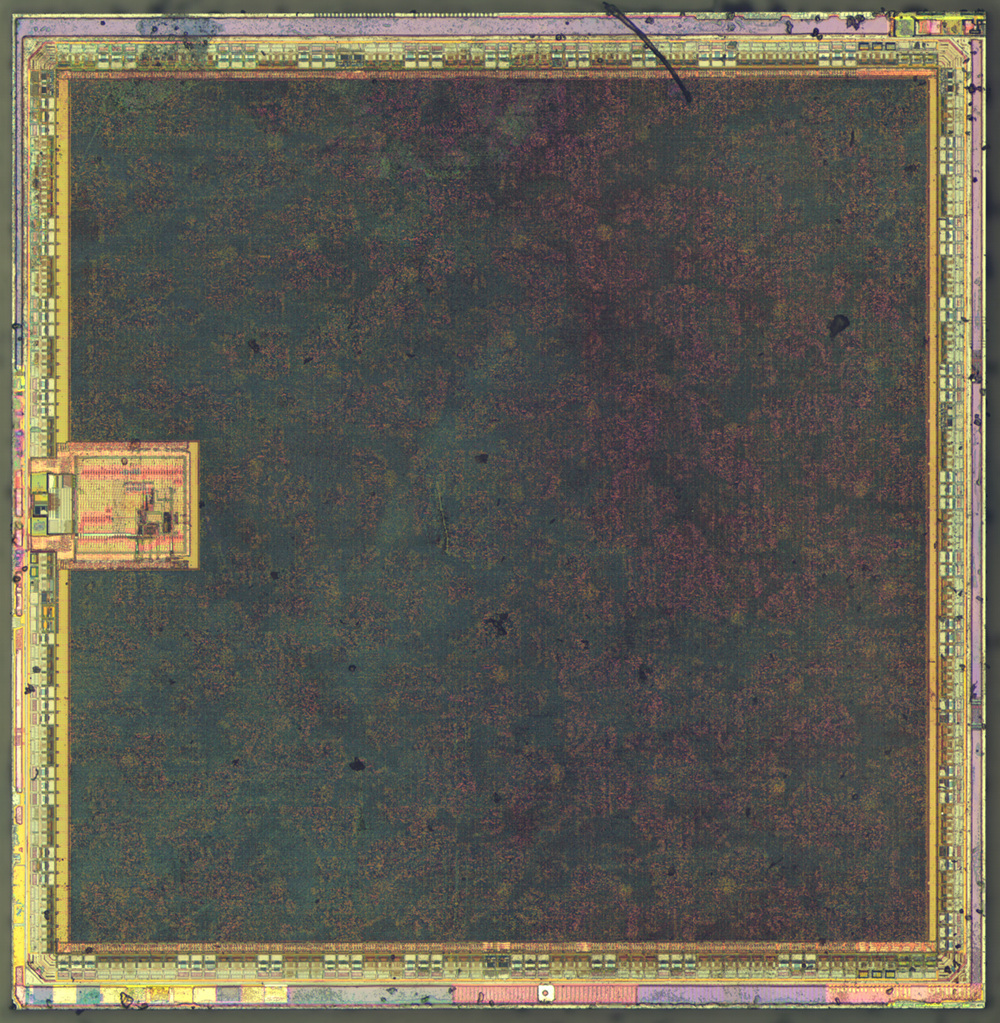

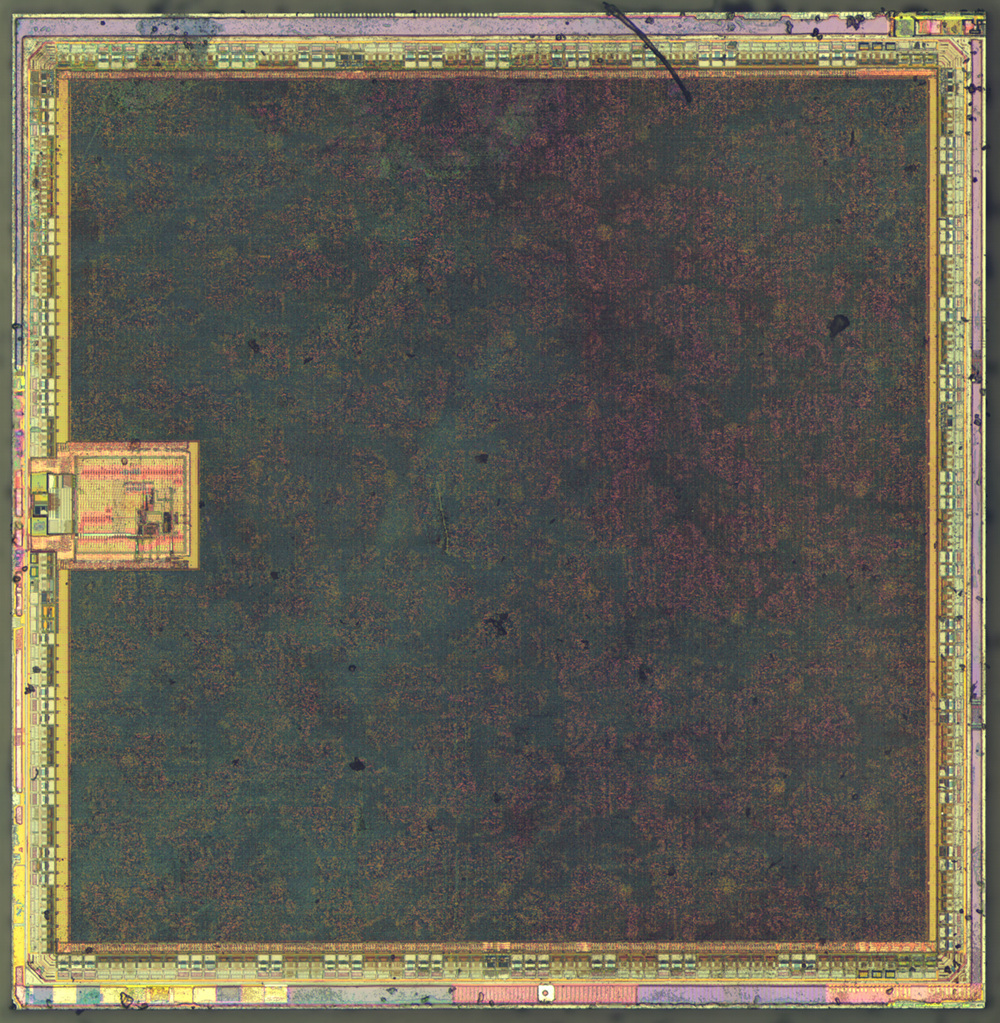

BarsMonster, вы делаете эти удивительные фотографии реверс-инжиниринг микроскопа на блоге?

Высокий, теперь это то, что я Cann СИС-порно! Ente |

|

|

10 июня 2013, 9:06:46 PM

10 июня 2013, 9:06:46 PM

|

# 4 |

|

Сообщений: 56

цитировать ответ |

BarsMonster, вы делаете эти удивительные фотографии реверс-инжиниринг микроскопа на блоге? Да, это я. |

|

|

10 июня 2013, 9:40:16 PM

10 июня 2013, 9:40:16 PM

|

# 5 |

|

Сообщения: 101

цитировать ответ |

Самое интересное для меня это окончательный вывод в блоге о плотности Avalon.

Можно ли сравнить его с ожидаемым клеток на основе чипа 28nm от KNC? Я имею в виду с точки зрения производительности / потребления? |

|

|

10 июня 2013, 9:42:52 PM

10 июня 2013, 9:42:52 PM

|

# 6 |

|

Сообщения: 1190

цитировать ответ |

Мммм, ASIC pr0n.

|

|

|

10 июня 2013, 10:05:50 PM

10 июня 2013, 10:05:50 PM

|

# 7 |

|

Сообщений: 56

цитировать ответ |

Самое интересное для меня это окончательный вывод в блоге о плотности Avalon. Можно ли сравнить его с ожидаемым клеток на основе чипа 28nm от KNC? Я имею в виду с точки зрения производительности / потребления? Грубым обратно из-расчетов огибающих показывает, что 28nm продукт должен быть ~ 10-15 раз больше энергии эффективной, немая реализация может повлиять на его на коэффициент по меньшей мере, 2-3. Таким образом, мы говорим о ~ 5 раз больше Mhash для той же потребляемой мощности. Но даже если он говорит, "на основе клеток"Я бы не стал ожидать, простую наивную реализации, учитывая, что количество труда для полного обычая Bitcoin-чипа дизайн не очень сильно отличается для 110nm / 65nm / 28nm. |

|

|

10 июня 2013, 10:46:45 PM

10 июня 2013, 10:46:45 PM

|

# 8 |

|

Сообщения: 588

цитировать ответ |

Кто знает, если проект Avalon щепы является своим родом "печатная копия" из Икара FPGA? Это может объяснить, почему он имеет структуру, как, что (из того немногого, что я знаю, НПЧ в основном то же самое, только больше и программируемый).

Кстати, это вероятность того, что вы не можете пойти ниже, чем процесс производства 110nm, если вы хотите сохранить температуру под контролем и поддерживать пакет QFN. Вот почему BFL пришлось переделать чип и использовать пакет FCBGA, с этой блестящей верхней поверхностью (очень уязвимом тоже, у них есть что-то от старой процессора AMD Athlon Palomino процессоров). Заимствование информации от других продуктов (т.е. систем на чипе, как на ARM Cortex) 28nm часто "умереть термоусадочные" существующего чипа 32нм, так что если Orsoc / КНЦ уже в состоянии сделать чип 32-нм не трудно думать, что первые прототипы будут использовать это больше (и менее эффективно) умирают, делая усадку, когда все -almost- отлично , Это "должно быть" лучше, я до сих пор помню, что произошло, когда Intel выпустила серию P4 Prescott ... Я забыл упомянуть, что чип BFL сделан Global литейные с производственным процессом 65нм, и кажется, что они были "некоторые проблемы" в прошлом... |

|

|

10 июня 2013, 10:49:50 PM

10 июня 2013, 10:49:50 PM

|

# 9 |

|

Сообщения: 154

цитировать ответ |

интересно увидеть поврежденный чип

|

|

|

10 июня 2013, 10:52:09 PM

10 июня 2013, 10:52:09 PM

|

# 10 |

|

Сообщений: 56

цитировать ответ |

Кто знает, если проект Avalon щепы является своим родом "печатная копия" из Икара FPGA? Это может объяснить, почему он имеет структуру, как, что (из того немногого, что я знаю, НПЧ в основном то же самое, только больше и программируемый). Нет, это не "печатная копия" ПЛИС. Это может быть основано на аналогичной реализации алгоритма, но это степень сходства. Кстати, это вероятность того, что вы не можете пойти ниже, чем процесс производства 110nm, если вы хотите сохранить температуру под контролем и поддерживать пакет QFN. Вот почему BFL пришлось переделать чип и использовать пакет FCBGA, с этой блестящей верхней поверхностью (очень уязвимом тоже, у них есть что-то от старой процессора AMD Athlon Palomino процессоров). Это не совсем верно. В CMOS вы можете всегда низкое энергопотребление на порядок величины за счет снижения напряжения питания & часы, а затем компенсировать это при использовании большего количества чипов (мощность падает нелинейно, так что есть выгода).Заимствование информации от других продуктов (т.е. систем на чипе, как на ARM Cortex) 28nm часто "умереть термоусадочные" существующего чипа 32нм, так что если Orsoc / КНЦ уже в состоянии сделать чип 32-нм не трудно думать, что первые прототипы будут использовать это больше (и менее эффективно) умирают, делая усадку, когда все -almost- отлично , Это "должно быть" лучше, я до сих пор помню, что произошло, когда Intel выпустила серию P4 Prescott ... Вы не можете просто сжать кубик на современные процессы, как это было возможно во времена 350-800nm технологий. Вы должны повторить почти все - там просто слишком много ограничений, и слишком много изменений с этим "всего лишь" 14% усадка. Я забыл упомянуть, что чип BFL сделан Global литейные с производственным процессом 65нм. Любые ссылки на кого попросить, чтобы получить чип образца от них? |

|

|

10 июня 2013, 10:53:24 PM

10 июня 2013, 10:53:24 PM

|

# 11 |

|

Сообщения: 280

цитировать ответ |

Отличная работа.

|

|

|

10 июня 2013, 10:56:54 PM

10 июня 2013, 10:56:54 PM

|

# 12 |

|

Сообщений: 95

цитировать ответ |

Интересно. Первый раз, чтобы знать кого-то есть инженерный китайский продукт.

|

|

|

10 июня 2013, 11:01:39 PM

10 июня 2013, 11:01:39 PM

|

# 13 |

|

Сообщений: 56

цитировать ответ |

Интересно. Первый раз, чтобы знать кого-то есть инженерный китайский продукт. Это второй раз для меня Недавно я смотрел на самый дешевый (5 $ доставленные) Китайский веб-камера - и это та же инженерия & логистики чудо (как на земле, они сумели выжать все это в 5 $?), как в новейших 22 нм продукции. |

|

|

10 июня 2013, 11:04:21 PM

10 июня 2013, 11:04:21 PM

|

# 14 |

|

Сообщения: 588

цитировать ответ |

[...] Я разрезал весь ответ просто сказать "благодаря", это очень интересно! Я немного "старомодный" и я признаю, что я пытался выяснить, используя информацию, которую я знаю о процессорах. котировка Любые ссылки на кого попросить, чтобы получить чип образца от них? Инаба / Josh может быть |

|

|

11 июня 2013, 3:43:06 AM

11 июня 2013, 3:43:06 AM

|

# 15 |

|

Сообщения: 742

цитировать ответ |

Тип микроскопа?

|

|

|

11 июня 2013, 3:46:05 AM

11 июня 2013, 3:46:05 AM

|

# 16 |

|

Сообщений: 56

цитировать ответ |

Тип микроскопа? Китайский оптический металлографический микроскоп BM-158J с 5-мегапиксельной камерой USB. (~ 60 выстрелов сшитые для 1 большого фото) http://3.14.by/en/read/microscope |

|

|

11 июня 2013, 3:54:44 AM

11 июня 2013, 3:54:44 AM

|

# 17 |

|

Сообщения: 742

цитировать ответ |

Тип микроскопа? Китайский оптический металлографический микроскоп BM-158J с 5-мегапиксельной камерой USB. (~ 60 выстрелов сшитые для 1 большого фото) http://3.14.by/en/read/microscope Удивительная работа |

|

|